Translation of the article:

Пилипенко В. А., Горушко В. А., Петлицкий А. Н., Понарядов В. В., Турцевич А. С., Шведов С. В. Методы и механизмы геттерирования кремниевых структур в производстве интегральных микросхем // Технология и конструирование в электронной аппаратуре.— 2013.— № 2–3.— С. 43—57.

\_\_\_\_\_

## UDC 539.2/6:539.216.1

## METHODS AND MECHANISMS OF GETTERING SILICON STRUCTURES IN FABRICATION OF THE INTEGRATED CIRCUITS

V. A. Pilipenko, V. A. Gorushko, A. N. Petlitsky, V. V. Ponaryadov,

A. S. Turtsevich, S. V. Shvedov

Element base integration rate increase presents ever more strict requirements to concentration reduction of the polluting impurities and oxidation defects of packing in the initial silicon wafers with its preservation in the process cycle of the IC fabrication. This governs the high application actuality of gettering in the modern technology of microelectronics. There were considered the existing methods of gettering the silicon wafers, as well as the methods of their progress.

Key words: silicon, getter, laser, fast diffusing impurity, center of gettering, dislocation, defect of packing.

Arrangement density increase of the integrated microcircuit (IC) elements ensues the stricter requirements to purity of the semiconductor materials, as presence of the crystal structure defects and metal impurities in it affects their functionality. Foremost, this concerns silicon, which is the basic material for IC fabrication. A great contribution to this is made by the point defects and polluting impurities, such as copper, iron, nickel, chrome, sodium, etc., resulting in the yield reduction of the good ICs due to the uncontrolled process of the defect formation in the active areas. The requirements to purity of the silicon wafers in bulk and by surface are being steadily made ever stricter parallel to reduction of the critical size of elements, reaching the detection limit when determining the surface concentration of metals and iron bulk concentration (see **Table 1**) [1]. Density parameter of the packing oxidation defects (POD) also serves the surface purity criterion, and the requirements to its value are quite strict. Reduction of the element sizes requires application of the new materials and technological processes of their fabrication, which results in expansion of the metals nomenclature and reduction of the critical value of their surface concentration. Thus, with the size of elements being 0,8 µm the critical concentration value for each of metals, forming silicides (Cr, Fe, Ni, Cu), constitutes  $1 \cdot 10^{11}$  atom / cm<sup>2</sup>. With transition to the sizes of less than 0,8 µm, this row is extended with Co, alkali metals K, Na, whose ions are mobile, as well as the alkaline earth element Ca and heavy metals Pt, Ir, Ba. The critical value of concentration for each of these elements constitutes  $\leq 1 \cdot 10^{10}$  atom/cm<sup>2</sup> [1].

the Dynamic Operational Memory Device

| F                                                    | Diameter of Wafer, mm |                   |                        |           |                |                        |

|------------------------------------------------------|-----------------------|-------------------|------------------------|-----------|----------------|------------------------|

| Feature                                              | 150                   | 200               | 200                    | 200       | 300            | 300                    |

| Minimum size of element, um                          | 0,8                   | 0,35              | 0,18                   | 0,13 0,09 |                |                        |

| Iron bulk concentration, atom / cm <sup>3</sup>      | 5·10 <sup>10</sup>    | $2 \cdot 10^{10}$ | $\leq 1 \cdot 10^{10}$ | ≤1⋅1      | $0^{10}$       | $\leq 1 \cdot 10^{10}$ |

| Metals surface concentration, atom / cm <sup>2</sup> | 1·10 <sup>11</sup>    | $2 \cdot 10^{10}$ | $\leq 1 \cdot 10^{10}$ | ≤1⋅1      | $0^{10}$       | $\leq 1 \cdot 10^{10}$ |

| POD density, cm <sup>-2</sup>                        | ≤6·10¹                | ≤2·10¹            | $\leq 4,4 \cdot 10^0$  | ≤2,8      | $\cdot 10^{0}$ | $\leq 1,6 \cdot 10^0$  |

The main sources of the polluting impurities are the accessories and equipment, used in the different technological processes of ICs fabrication [2]. In principle, material pollution starts already in the growth process of the silicon mono-crystals by the Chokhralsky method. The sources of impurities here are the initial poly-crystal silicon, quartz crucible and the furnace itself [3]. However, meanwhile the grown ingots are considered pure enough, as the impurities concentration is not high: Fe, Cu and other metals are of the numerical values of less than  $10^{14}$  cm<sup>-3</sup> [4].

The major polluting operations during fabrication of substrates are the mechanical slicing and polishing. This is pointed out by distribution of the metal impurities in the wafers — their grater part is localized in the near surface layer with the thickness of the order of a few micrometers from the surface [2].

Pollution with the uncontrollable impurities occurs also during the multiple heat treatments in the diffusion furnaces, to which a silicon wafer is subjected in the process of IC creation [2]. At the high temperature the quartz reactors let the metal atoms «pass», evaporating from the internal surface of the surface metal parts (usually Fe, Ni, Cr, Cu), which afterwards diffuse into the wafer bulk [4]. In the plants for the epitaxial growth of wafers the potential source of impurities is a graphite heater, that in the heating process emits the transitional metals, for instance Fe, Ti.

Pollution probability of the silicon wafers with the metal impurities is also evident during cleansing, rinsing, transportation of wafers [5], ion implantation [6] and plasma chemical treatment [7]. As a

result, concentration of the metal impurities in the silicon wafer bulk during the heat treatment process

may reach 10<sup>18</sup> cm<sup>-3</sup>, and in the near surface area it is one – two orders higher [2, 7]. As during the

temperature reduction solubility on many metals reduces in silicon, their concentration during the wafer cooling supersedes the solubility limit, and this causes their diffusion to the wafer surface, precipitation and complex formation of metals with the doping impurities [8]. Formation of metal precipitates

affects the parameters of both bipolar and MOS-devices. Small metal precipitates (from 5 to 20 nm)

are the sources of the current leakage in the bipolar transistors [9] and the source of the localized

breakdown in the thin oxide films [10]. As the centers of the heterogeneous nucleation, required for

precipitation, there may serve defects of the crystal structure, such as dislocations, defects of packing

(predominantly on the partial dislocations) and oxygen precipitates. Packing defects, decorated with

the metal impurities, also cause the leakage currents rise and breakdown of the thin oxide [10].

Influence of the transitional metals, such as Fe, Ni, Cu, Cr on yield of good ICs and their reliability at the technology level of 0,5 um becomes noticeable with the concentration of, for instance, Fe ions of the order 10<sup>11</sup> cm<sup>-3</sup>. Also, it is assumed, that when the capacity of the random access memory devices becomes close to Gb with the thickness of the gate oxide of 7,5 nm, the limit of the permissible iron concentration will fall to the level of 10<sup>10</sup> cm<sup>-3</sup> [4].

It is possible to substantially reduce the amount of the uncontrollable impurities in the silicon wafers, introduced in the process of the entire cycle of ICs fabrication by means of applying the appropriate measures. For instance, this may be the temperature reduction in the process of the periodical high temperature cleansing of the quartz pipes in the medium of HCl, utilization of the advanced furnace designs, for instance, double pipes, displays [11]. Chemical treatment of wafers prior to thermal treatment in the mixtures of H<sub>2</sub>O<sub>2</sub> and HCl, HF and ethanol makes it possible to reduce the amount of metal pollutions on their surface [12]. Besides, replacement of components of the ion implantation plants, plasma chemical etching, made of the stainless steel, for aluminum, silicon and carbon made substantially reduces the overall pollution level [2].

However, all this does not make it possible to avoid pollution of the silicon wafers with the uncontrollable impurities and generation in them of the point defects in the process of fabrication of the semiconductor devices. In view of this, at present of great significance for this purpose acquire the process methods — methods of gettering [2, 13]. They make it possible to create in the silicon wafer the pure from the structural defects and the polluting mechanical impurities near surface area, in which are formed the active and passive elements of the IC areas. According to [1], gettering is the process of dissolving the unadvisable impurities with their subsequent diffusion and precipitation in the specially created zones of wafers — getters, where they do not exert the detrimental influence on operation of the device. A getter is capable of grasping and keeping the fast diffusing impurities and point defects, as well as creates the conditions, ensuring their high mobility [14].

During fabrication of the contemporary microelectronic devices the problem of purity becomes one of the most global ones, meanwhile what is meant is purity at all stages of the overall cycle of their fabrication. Therefore quite actual is the search of recommendations for the correct selection of the method of gettering in the various cases. For this in the present article are classified the existing methods of gettering with the analysis conducted of the methods of their passing.

There exist the various methods of gettering, differing with location of a getter relative to the operational side of the wafer, the gettering phase and the method of its creation [15].

Getter may be located outside the wafer, on the non-working side of the wafer, on the working side between the elements, in the bulk of the wafer. As a rule, the preference is attributed to the first two methods.

In order to obtain the solid gettering phase the following methods are used:

- mechanical introduction of irregularities

- by abrasive treatment;

- by sand blasting treatment;

- by impact treatment;

- formation of film on the wafer's surface

- of porous silicon;

- admixture-silicon glass;

- poly-silicon;

- thermal and pyrolytic film of SiO<sub>2</sub>;

- irradiation of the surface

- ion doping;

- laser irradiation;

- ion implantation of inept gases;

- diffusion doping;

- annealing as per the preset program.

Gettering by the gaseous phase is used during the wafer annealing in the various media:

- annealing in vacuum;

- annealing in the inept medium;

- annealing in the chlorine containing medium.

Gettering by means of the liquid phase is used during application of

- the amorphous liquid phase;

- fustible eutectic.

Amongst the methods with location of the getter outside the wafer of wide application are the methods, based on extraction of the point defects to the gaseous phase and to vacuum. In [16] it is established, that annealing of the silicon wafers and ingots prior to oxidation influences generation of the packing defects. Performance of the preliminary annealing of the wafers at the temperature of 800— $1200^{\circ}$  C in the argon atmosphere reduces density of the packing defects in them, meanwhile the size of defects does not depend on the time of annealing. This is determined by resorption in process of such treatment of the growth defects and migration of their constituting atoms to the surface, being a drain for them. Thus, the pre-oxidation high temperature annealing makes it possible to create the layer in the near surface area, practically free from the packing defects. Thickness of this layer depends on the annealing time (t), and incubation time (t) — on the initial length of the surface packing defects and the annealing time. With  $t > t_n$  thickness of the area, vacant from the given defects (d), varies as per the law  $d \sim t^n$ , where  $n = 0.63\pm0.06$ .

The efficient method of gettering is introduction of the mechanical irregularities into the reverse side of the wafer, which are done mostly by grinding [17], sand blasting treatment [18], diamond polishing [19]. N this case gettering is determined by damages of the crystal lattice, which are capable of eradicating the defect buds and adsorbing impurities at the time of the high temperature treatment. For instance, grinding of the reverse side of the substrate prior to oxidation reduces density of the packing defects by three orders. However, on the other side, creation of the disturbed layer results in

emergence of dislocations in the epitaxially grown layers and their gettering of the fast diffusing impurities. Besides, the gettering layer causes the curve of the semiconductor wafers, and the rough reverse side grasps the impurities during the chemical treatment and thus pollutes the wafer. It is also noteworthy noticing, that the mechanical treatment is usually performed prior to the fabrication process of the semiconductor devices, consequently, at the time of the high temperature treatments there occurs a partial re-crystallization of the disrupted layer, resulting in release of its grasped impurity [20].

In order to preclude the given phenomena in [21, p. 8] the following method of gettering was offered. In the reverse side of the wafer by means of grinding the disruptions of the crystal lattice are introduced for the depth of 8—25 um. Then the wafers are subjected to annealing in the inept medium at the temperature and duration of the process, sufficient for gettering the fast diffusing impurities and release of the mechanical stresses. After the thermal treatment the prompt cooling is performed, and further the both sides of the wafer are polished up to the unruffled surface. As a result, on the side of the wafer, in which the irregularities were introduced, under the unruffled surface the disrupted layer remains, gettering the point defects during the subsequent technological processes.

Amongst the contemporary methods of gettering with use of the mechanically disrupted layer is the hydro-abrasive gettering [1]. This method is attractive, as it is easily embedded into the technology of the chemical-mechanical polishing of the silicon wafers, because a getter is created on the reverse side of the of the ground-etched wafer, and formation of the gettering centers and the process of gettering proper occur simultaneously with the first thermal oxidation. The basic variable parameters of the process are the pressure of the hydro-abrasive stream at the nozzle exit, which may vary within the limits of 200—500 kPa, as well as the distance from the nozzle to the wafer surface. Other parameters of the process – the angular velocity of displacement of the table with the wafers, the frequency of the nozzle oscillations, composition of the applied abrasive are constant. The given method is quite effective — it makes it possible to reduce density of the micro-defects (small etching pits) by two orders and by two-three orders – defectiveness of the gate dielectric.

One more method — pre-oxidation gettering [16, 22] is in creation of the stressed layer by means of applying aluminum oxide or silicon nitride with the subsequent annealing, promoting diffusion to it of the point defects. Efficiency of gettering depends on thickness of the stressed layer, time and temperature of annealing and increases, if prior to the film oxidation to the reverse side of the wafer by means of the phosphorus diffusion to introduce the non-conformance dislocation. In order to attain the maximum efficiency, thickness of the applied layer of silicon nitride should constitute 200—400 nm, and annealing of the wafer to be conducted in the inept medium within 1—4 hours at the temperature of 1000—1200 °C. The non-conformance dislocations are created by means of phosphorus diffusion at 1050—1150 °C during 1—7 hours. The stressed layer and the non-conformance dislocations, formed in the initial wafer, getter both the available in it point defects and the introduced ones

during the subsequent treatments. It is noteworthy marking, that for the gettering of of the impurity defects by means of the phosphorus diffusion, its concentration should not obligatorily ensure formation of the non-conformance dislocations, as the diffusive layer without dislocations also possesses the gettering action [23], however, smaller, than with the dislocations.

Gettering of the fast diffusing admixtures may be conducted by means of the thin layer of the porous silicon, formed on the reverse side of the wafer by the anode treatment in the etching acid [24]. The given films possess the effect of gettering owing to their high specific surface and the high mechanical stresses on the boundary with silicon [25]. Of such properties are the films of the poly-crystal silicon [26] and germanium [27].

Popular is the method of gettering with application of the phosphorus doped diffusion layer [28], which is created on the reverse side of the wafer prior to the oxidation process. It was established, that the effect of gettering in this case exist and without the non-conformance dislocations and depends on the phosphorus concentration [29]. Efficiency of the process becomes considerable, if the phosphorus concentration exceeds  $10^{20}$  cm<sup>-3</sup>. With the phosphorus concentration of  $10^{21}$  cm<sup>-3</sup>, concentration of gold in the wafer bulk reduces to 1000 times because of formation of the ion pairs between gold and phosphorus [30]. It is to be noted, gettering is possible by the boron doped diffusion layers, however, efficiency in this is smaller, than in the case of the phosphorus doping [26].

Of the gettering properties are also the silicon layers, disrupted by the ion doping [31]. Efficiency of such layers is determined by the type of the implanted ion and reduces in the row of O, P, Si, As, B [32]. The type of disruptions is determined by the kind of ions, dose, energy, existence or absence of the oxide protective film, temperature of the wafer during the ion implantation, orientation of the wafer and the annealing mode [33]. At the time of annealing the disrupted layer there are formed the dislocation loops, the packing defects, which act as the centers of gettering. Thus, disruptions of the crystal lattice, created by the ion doping, are used for gettering the polluting impurities from the targets of silicon imaging devices. For the satisfactory operation of the target the leakage current of one diode should not exceed  $5 \cdot 10^{-14}$  A at the voltage of 30 V (diodes with the increased leakage currents produce the dark spots on the video image). The main cause, resulting in occurrence of the leakage currents, was formation of the non-coherent precipitates of the polluting impurities. For gettering into the reverse side of the wafer were introduced the ions of phosphorus, arsenic, argon with the energy of 50 keV and the various doses with the subsequent annealing in the dry nitrogen with addition of O<sub>2</sub> during 30 min. The comparative analysis of the gettering effect showed, that the video-defects vanish with the phosphorus doping doses —  $10^{16}$  cm<sup>-2</sup>, arsenic —  $10^{15}$  cm<sup>-2</sup> and argon —  $3 \cdot 10^{15}$  cm<sup>-2</sup>. The important peculiarity of such kind of gettering is, that it passes at a high speed at the relatively low temperatures. Thus, a film of gold with the thickness of 0,15 um, applied on the reverse side of the wafer, during 16 hours of annealing at the temperature of 500 °C completely dissolves, diffuses through the wafer with the thickness of 250 um and crystallizes in the kind of individual grains on the argon implanted (10<sup>16</sup> cm<sup>-2</sup>, 250 keV) side of the wafer.

Ion doping is also applied for creation of the internal gettering layer, located somewhat deeper the future device area (about 0,8 um for the designed at the present time ICs). In such a case the drains for the fast diffusing admixtures are the structural silicon defects, created in the substrate's bulk [34]. On efficiency of the internal gettering the following factors exert influence [35]:

- density of the small defects in the substrate's bulk, playing the role of drains for the detrimental impurities;

- availability of the near surface layer, free from the crystal defects, worsening quality of the electronic devices;

- preservation of the gettering centers in the wafer's bulk during the entire process of IC creation.

One of the most acceptable methods of creation of such a gettering layer, possessing the high efficiency (as the drain area for the admixture atoms), is implantation into the working surface of the silicon wafer of hydrogen or helium at the room temperature with the subsequent annealing at the temperature of 800—900 °C during from several dozens of minutes to one hour [36]. Such a procedure results in formation of the layer containing the gas bubbles at the depth, in conformance with the project run. This is determined by the low solubility of the implanted atoms in silicon, what promotes their segregation into the small gas vacation complexes already at the implantation stage. The subsequent annealing results to growth of such complexes and formation of bubbles. The implanted into silicon hydrogen or helium may during annealing leave the area of bubbles, penetrate the surface layer of silicon and evaporate from the surface already at the temperature, far below the melting point [37]. And this means, that in dependence on the gas concentration and the conditions of annealing, it is possible to obtain the layer, containing interstice, actually not containing the gaseous phase. The similar defects are very efficient drains (traps) for the unadvisable impurities. The ruptured chemical ties on the internal walls of interstice grasp the impurity atoms, which results in emergence of gradient in distribution of their concentration near the layer, containing the interstice. This gradient plays the role of the moving force, stimulating diffusion of impurities from the devices area to the great area, to the area of interstice. For the several types of impurities their concentration may be lower by several orders [37].

Other approach to creation of the internal getter, well compatible with the technology of IC fabrication, is creation of the oxygen precipitates with silicon in bulk of the silicon wafer, being efficient drains for the alien impurities, and creation of the defectless near surface zone (pure zone) for formation of the active IC structures. Pure zone and the layer of the bulk defects — these two most important factors, governing efficiency of the internal gettering, which was demonstrated way back in 1970—80 years [38, 39]. The generally recognized formation pattern of such a getter is the definite heat treatment conductance sequence of the silicon wafers [40]. The first heat treatment, high temperature (1100—1200°C) one, is intended for formation in the near surface area of the zone wafer, depleted by oxygen (because of its evaporation). The second heat treatment, low temperature (600—800°C) one, is

intended for origination of the oxygen precipitation centers. At the third stage, high temperature (>900°C) one, on the oxygen precipitation centers, disintegration occurs of the oxygen solid solution and growth of the oxide precipitates, serving drains for the unadvisable impurities from the working areas of the wafer.

At the last time the method of developed of creation of the oxygen precipitates in silicon, the so called magic depleted area, based on the accelerated oxygen precipitation in the areas, enriched with vacancies (the definite vacation profile is created by means of the fast thermal annealing [1]. Differences of the formation mechanism of the depleted with micro-defects near surface area in this case from the traditional method is in the following. In the traditional method of the internal gettering concentration of vacancies in the wafer's bulk is small and constant by the wafer's thickness, while concentration of the internode oxygen is great in the wafer's bulk and diminishes to the surface. In the formation method of the magic depleted zone the situation is different: concentration of the internode oxygen is permanent by the wafer's cross-section, and concentration of the «hardened» vacancies is great and constant in the wafer's bulk and diminishes to the surface. In the traditional method of the internal gettering there may be used only those silicon ingots (or its parts),in which concentration of the internode oxygen is within the limits  $(7,5-9,0)\cdot 10^{17}$  atom/cm<sup>3</sup>, when the precipitation process is steady and the bulk density of precipitates reaches 10<sup>11</sup> cm<sup>-3</sup>. While resorting to the second method of the oxygen concentration, the thermal prehistory of obtaining the ingot and the location of the sliced from it wafer is of no significance. Besides, efficiency of the second method practically does not depend on the thermal cycle of obtaining the device structures. When creating the internal getter by this method there forms the deeper with a sharper boundary, the depleted near surface area (50-60 µm), suitable, opposite to the traditional method, for creation of the structures with the slit isolation.

An interesting method of gettering was offered in [41]. Unlike the methods, when the undesirable impurities although are removed from the working areas of the semiconductor wafer, but nonetheless are available in their vicinities, here the method is used, applied for the zone cleaning of the silicon ingots from the admixture matters in the solid state: under influence of the temperature gradient the impurity is removed to the ingot's butt surface and then etched off. An indirect confirmation of suitability of this idea for gettering the impurity in the semiconductor wafers is movement of the oxygen atoms under influence of the temperature gradient during formation of the buried layers of SiO<sub>2</sub> by means of the non-isothermal annealing of the ion-doped with oxygen of the silicon areas. Simulation of such process showed, that irrespective of the initial distribution of the impurity in the near surface area, under influence of the temperature gradient it concentrates on the wafer surface and can be removed with the subsequent etching of the surface layer off.

The original approach for purification of the silicon wafers' bulk from the undesirable impurities is described in [42]. It is based on application of the ultrasonic treatment of the wafers at the room temperature at the frequency of 0,4—1 MHz and duration up to 6,5 hours. As the strongest influence

ultrasound exerts on the near surface area of the wafer (depth about  $100 \mu m$ ), as a result of such treatment there occurs the stimulated by ultrasound migration of atoms of the alkali metals K, Na from the bulk to the surface. After removal of the surface layer this makes it possible to considerably reduce concentration of the alkali metals in the silicon wafer.

It is to be noted, however, that the methods, which are related to cleaning the bulk of the silicon wafers from the undesirable impurities by means of their transfer to the surface layer with its subsequent removal, cannot be applied at any from the IC fabrication process stages. Due to this cause they remained in low demand during the ICs creation, but find a wide application for study of the control processes of the defect formation in the semiconductor material.

But also the methods of the internal gettering have the considerable limitations and not always can be applied or not always turn out to be effective. This takes place, for instance, in the cases, when:

- are used the mono-crystals with the oxygen contents of less than  $5 \cdot 10^{17}$  cm<sup>-3</sup> or the high-doped silicon wafers of n-type (arsenic or antimony doped), when the precipitation process does not happen;

- are applied the low temperature processes or the fast thermal treatment, when the weakly diffusing atoms of the internode oxygen cannot cover the great distances during the treatment time;

- for creation of the devices is used the entire thickness of the wafer (power devices).

In such cases it is required to apply the external gettering or use combination of the external or internal gettering.

Amongst the used at present methods of the external gettering the most interesting is the well-controlled method of introducing disruptions into the reverse side of the wafer by means of the high energy laser irradiation [43—46]. Meanwhile there occurs the silicon evaporation with formation of the shallow pits, located close to each other, which results in generation of the crystal lattice disruptions and emergence of the mechanical stresses. After irradiation the wafers are subjected to annealing, sufficient for formation of dislocations around the disrupted areas and diffusion to them of the mobile point defects and metal impurities from the wafer's bulk. The important peculiarity of this method is a possibility of formation of a getter at the various stages of the IC creation. Besideso, during formation of a getter on the initial silicon wafers its serviceability may be maintained during the entire process cycle of the ICs fabrication [47, 48].

The depth of disruptions, caused by the laser treatment, during increase of the energy density up to 7 and after 8 joule/cm<sup>2</sup> rises in the linear way, in the interval of 7—8 joule/cm<sup>2</sup> there occurs a sharp jump, which is related with a transition from the silicon melting to its evaporation. During the laser irradiation with the energy blow this range, there happen the surface melting and its subsequent epitaxial re-crystallization, not causing generation of the crystal defects. The laser treatment with the energy higher than the indicated one, results in the silicon evaporation and the subsequent re-crystallization occurs already with formation of the poly-crystal silicon. The emerged during this de-

fects consist of the dislocations of two types [45]. On the periphery of the laser spot there observes a high concentration of the sliding dislocations, which well annihilate during annealing. They are similar to dislocations, emerged during the mechanical methods of disrupting the crystal structure of the wafer. But under the area, subjected to the laser influence, by means of the electron microscopy there were detected the micro-cracks, which get annealed in the process of heat treatment, and the related to them rows of the fixed dislocations, being thermally stable [46]. The energy threshold, when there occurs formation of the micro-cracks on silicon of orientation |111|, constitutes approximately 15 joule/cm² with the pulse duration of 100 ns. The thermally stable lattice defects at the time of the subsequent thermal treatments act as drains for the point defects.

Concentration defects in silicon is characterized by the life time of the minority charge carriers  $\tau$ . **Table 2** lists the values  $\tau$ , obtained after oxidation of ten wafers, one half of which was laser treated. From these data it ensues, that to obtain the effect of gettering the minimum energy density should be not less than 8 joule/cm<sup>2</sup>, to which corresponds the disruption depth of h=5 µm. While increasing the disruptions depth efficiency of gettering rises, however, with h=20 µm (E= 33,3 joule/cm<sup>2</sup>) the life time  $\tau$  after heat treatment reduces. This is related to slide of dislocations through the entire thickness of the wafer to its working side. Therefore the optimum for gettering one should consider the depth of disruptions of 5—10 µm, which is attained at E=9—15 joule/cm<sup>2</sup>.

Table 2 Efficiency of wafers treatment with the laser irradiation of different power [46]

| E,                      | Values τ for a part of a wafer, μs |                          |  |  |

|-------------------------|------------------------------------|--------------------------|--|--|

| Joule / cm <sup>2</sup> | irradiated                         | without irradia-<br>tion |  |  |

| 9,9                     | 280,3                              | _                        |  |  |

|                         | 190,0                              | 100,8                    |  |  |

| 8,2                     | 277,4                              | 103,3                    |  |  |

|                         | 606,7                              | 3,2                      |  |  |

| 6,5                     | 35,0                               | 8,6                      |  |  |

|                         | 11,7                               | 40,7                     |  |  |

|                         | 94,5                               | 211,7                    |  |  |

| 5,3                     | 7,4                                | 9,4                      |  |  |

|                         | 42.3                               | 70,9                     |  |  |

|                         | 79,6                               | 9,4                      |  |  |

Meanwhile, it is worth to note, that the laser irradiation of nanosecond duration results is the silicon expelling from the irradiation influence area that causes pollution of the working side of the wafer with the silicon dust. Therefore for creation of the gettering area of interest is the laser treatment

in the mode of the heat flow (by a continuous laser irradiation), ensuring silicon melting without its evaporation.

Such an approach was realized for creation of the gettering layer from the non-working side of the silicon wafer during application of the A $M\Gamma$ :Nd<sup>+</sup> laser in the continuous mode of operation. In this case a silicon wafer develops the tensile stresses, whose value reduces with the scan rate increase V and reduction of the power density  $E_{M0}$  of laser irradiation (**Table 3**) [49, 50].

Table 3 X-Ray topograms of Si-wafers after their laser treatment

| Modes of Laser<br>Treatment                                       | Topograms of Si-wafers, treated at various modes |                                             |  |

|-------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------|--|

| $E_{\text{M0}} = 5 \cdot 10^5 \text{ W/cm}^2,$<br>V = 60  cm/sec, | H = 200 um                                       | H = 400 um                                  |  |

| $E_{\text{M0}} = 5 \cdot 10^5 \text{ W/cm}^2,$<br>H = 200  um     | V = 40 cm/sec                                    | V = 60 cm/sec                               |  |

| V=60 cm/sec,<br>H = 200 um                                        | $E_{\rm M0} = 4.5 \cdot 10^5  \rm W/cm^2$        | $E_{\rm M0} = 5 \cdot 10^5 \mathrm{W/cm^2}$ |  |

In [51] on the basis of the performed calculation of the temperature fields and experimental results there was determined the required from the point of view of efficiency and overlapping of the stressed areas from the two adjacent scan lines, the mode of laser treatment for formation of the gettering layer: H = 200—240 um,  $V \approx 60$  cm/s and  $E_{\text{M0}} \approx 5,5 \cdot 10^5$  W/cm<sup>2</sup>. The subsequent prolonged thermal treatment at the temperature of 1100—1200°C in the oxygen medium results in the efficient formation in the area of the laser influence of the dislocation lattice and oxygen precipitates, being the centers of gettering (**Table 4**).

| Modes of                      | Temperature of thermal treatment |        |        |  |

|-------------------------------|----------------------------------|--------|--------|--|

| laser treat-<br>ment          | 900°C                            | 1150°C | 1220°C |  |

| V=40<br>mm/sec,<br>H = 200 um |                                  |        |        |  |

| V=60 cm/sec,<br>H = 200 um    |                                  |        |        |  |

| V=60 cm/sec,<br>H = 400 um    |                                  |        |        |  |

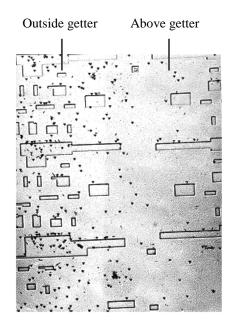

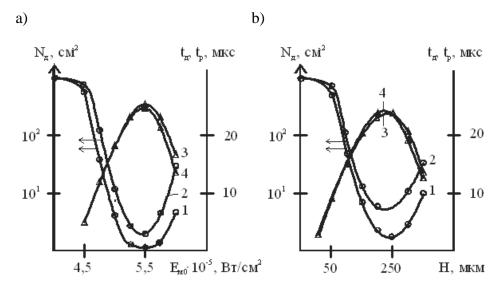

Creation of such gettering layer prior to the thermal oxidation at the temperature, exceeding the temperature of the subsequent extended high temperature processes, ensures a 220—440 times reduction of the packing defects and dislocations density (**Fig. 1**), to have a 2,9 times reduction of the fill-up ratio with the slide lines in the epitaxial films, to have a 12 times rise of the life time of the minority charge carriers and the recombination life time in silicon (**Fig. 2**), as well as to reduce 1,8 times the density of the surface states on the separation boundary «silicon — thermal silicon dioxide» [52, 53]. The thermally grown on such wafers the silicon dioxide films possess the improved structure, a higher charge stability and the high quality separation boundary.

Application of gettering with application of the continuous laser irradiation in the technology of creation of the bipolar ICs makes it possible at the expense of the propagation reduction of the slide lines, reduction of the dislocations density in the epitaxial film and exclusion of the conducting shunts emergence in the area of the active and passive elements to eradicate degradation of the breakdown voltages «collector — emitter» and the consumption currents. This ensures a two times increase in the yield of the good devices on the wafer and a 11,6% rise in the yield of the good devices after their assembly and measurement of the electric parameters [54]. In creation of the MOS IC such a method of gettering makes it possible at the expense of the threshold voltage reduction, determined by the charge

reduction on the separation boundary «Si —  $SiO_2$ », to exclude its degradation and, consequently, to increase (1,5 times) yield of the good devices.

Fig. 1. View of the decorated surface of the epitaxial silicon film after gettering

Fig. 2. Dependencies of the electro-physical parameters of Si-wafers after gettering on the power density of the continuous laser irradiation (a), pitch (b) and scan rate (c): 1 — density of packing defects  $N_{\rm A}$ ; 2 — density of dislocations; 3 — life time of the minority charge carriers  $\tau$ ; 4 — recombination life time  $\tau_{\rm p}$

In order to clean the working side of the silicon wafers from the admixture impurities of interest is the treatment mode by the laser irradiation of nanosecond duration (20—30 nsec), when melting occurs of the surface layer and its subsequent re-crystallization without introduction of any disruptions into the crystal lattice of this layer [55—57]. Analysis of such wafers' surface after the thermal oxidation shows, that after removal of the oxide film and etching the surface in the selective etchant the structural defects are not in evidence, peculiar for the thermal oxidation of the untreated wafers. This is related to the fact, that during melting of the thin surface layer there occurs its purification from the ions of metals and carbon owing to their diffusion via the liquid flux to the surface and the subsequent evaporation, as well as eradication of the upset by the chemical-mechanical polishing surface layer (**Table 5**) [56, 57]. This is confirmed by the results of the comparative analysis of the structure of dielectric films, cformed by means of the thermal oxidation in the dehydrated oxygen medium of the silicon wafers of the *n*-type conductivity, before and after the laser treatment of the surface.

Table 5

Surface structure of the silicon wafers, subjected to the chemical-mechanical and mechanical polishing before and after treatment with nanosecond pulses

| Performed t                          | reatments                    | Micro-reliefs of surfaces | Images of diffraction |

|--------------------------------------|------------------------------|---------------------------|-----------------------|

| Chemical-<br>mechanical<br>polishing | Before<br>laser<br>treatment |                           | ·                     |

|                                      | After<br>laser<br>treatment  |                           |                       |

| Mechanical polishing                 | Before<br>laser<br>treatment |                           |                       |

|                                      | After<br>laser<br>treatment  | }                         |                       |

Surface structure of the silicon wafers after treatment with the laser pulses is more uniform, as the wafer surface has no disrupted layer and ion admixtures, which result in the increased vapor formation and disruption of continuity of the formed layer, as well as create the crystal phases. About purification of the surface layer from the ion impurities after the laser treatment indicates reduction over two times of the fixed charge on the separation boundary «silicon — thermal silicon dioxide», as well as the spectra of the fast surface states, whose density in the middle of the denied zone in the section with the laser treatment is two times less, than in the untreated one [53].

However, application of such cleaning is limited, as it cannot be used at the different stages of IC creation — it can be conducted only on the initial wafers, prior to the moment, when on the surface there will be formed any functional layers.

Thus, application of the laser irradiation of nanosecond duration makes it possible to conduct purification of the working surface of the initial wafer from the ion impurities. For the efficient purification of the surface layer from the working side of the wafer from the uncontrolled impurities by means of gettering the most prospective is application of the continuous laser treatment for the controlled formation of the of the gettering centers from the non-working side of the wafer. The important advantage of such method is the possibility of its application at the various stages of ICs creation, and absence of any requirements on the special preparation of wafers points out its application justification in the VLSI technology.

Majority of methods of gettering was found by the empirical way and used in the ICs fabrication technology without determining a mechanism of their passing. For the considered above methods of gettering we will determine the possible mechanisms of interaction of the admixture defects with the point ones, being for them drains in the process of gettering.

As the admixture defects introduce the elastic tensions into the surrounding them matrix, their interaction with the external tensions brings movement and a build-up of the admixture defects in the areas of point defects.

The external tensions may have the macro- and micro- and non-homogeneous nature. The first, so called macro- non-homogeneous external forces, act on the entire ingot or a wafer. N case of the silicon wafer they emerge during application on its reverse side of the films  $Si_3N_4$  and  $Al_2O_3$ . Thus, for instance, in the film of  $Si_3N_4$  the internal tensions reach  $10^9$  N/m<sup>2</sup> and are balanced with the elastic tensions in the silicon wafer, which, in their turn, cause the directed movement of the admixture defects.

Tensions of the micro- non-homogeneous nature in silicon are caused by the linear, flat and bulk defects. Interaction of these defects with the admixture ones may be subdivided into the four kinds: those, caused by the difference in the sizes of the admixture defects and atoms of the matrix (array); caused by the difference in the elasticity models; chemical ones; electric ones. They all result in the non-uniform distribution and concentration of the admixture defects near dislocations, boundaries of grains, etc. Extrusion of the excessive admixture defects starts at the edge dislocations, and with their great saturation – at all dislocations, and this means, that with the small saturations the nuclei at the edge dislocations determine the entire kinetics of extrusion.

The high density of dislocations is attained by means of the high temperature phosphorus diffusion [58], ion implantation [59, 60], mechanical treatment [61—63], laser irradiation [47, 48]. Meanwhile, the energy and doze of ion implantation, as well as density of the laser irradiation energy should be sufficient for their formation.

Investigation of the copper gettering by means of the ion doped layer [61] showed, that dislocations with the Burgers vector b=a/2<110> possess a great capacity for the copper gettering, than the partial Frank dislocations with b=a/3<111>, which is accounted for by their great energy of the elastic field. In [61] it was established, that with the doze of ion implantations up to  $6\cdot10^{13}$  cm<sup>-2</sup> there emerge the packing defects, surrounded by the partial Frank dislocation, and the packing defects with the dislocation loops transform into the full dislocations with b=a/2<110>, which with a higher implantation dose for the dislocation grid. A considerable efficiency increase of gettering occurs with the dose of  $3\cdot10^{14}$  cm<sup>-2</sup>, when there is a great density of dislocations. Efficiency of such gettering in [61] was assessed by the relaxation leakage current of the disbalanced MOS-capacity. Increase of the leakage currents with the doses of  $3\cdot10^{15}$  and  $6\cdot10^{15}$  cm<sup>-2</sup> as compared with a dose of  $3\cdot10^{14}$  cm<sup>-2</sup> is explained by precipitation of the implanted impurity at dislocations. I. e. the required component of the microstructure of the gettering ion-doped layer is availability of dislocations with b=a/2<110>. Density of these dislocations with the high free energy, ensuring the efficient gettering, is assessed as  $2\cdot10^8$  cm<sup>-2</sup>.

If the impurity defects create the charged centers, i. e. are the donors or acceptors, then on their distribution exerts influence concentration of electrons or holes. Consequently, creating the nonuniform distribution on the wafer of the donor or acceptor impurity in the sufficiently great concentrations, one can expect the non-uniform distribution on the wafer and other charged admixture defects, for instance, the fast diffusing metals. Thus, it is possible to getter the undesirable admixture defects from the ICs active areas into the specially doped non-active areas. Phosphorus gettering of gold takes place as per the given mechanism. Gold takes mainly the replacing position, and vacancies interact with the phosphorus atoms with formation of the *E*-centers [64]. Gold dilution in silicon of its inherent conductivity occurs with interaction of the atoms of gold with the free vacancies, which was experimentally confirmed by means of the leakage current control of diodes after the subsequent operations of heat treatment of the wafers [58]. The considered mechanism of gettering is applicable not only for gold, but for other heavy metals as well [65]. The low temperature (800°C) gettering with phosphorus is effective in that case, if silicon does not contain precipitates of heavy metals. If such precipitates are available. Then for their dilution annealing is required at the high temperature (1000°C). Thus, the diffusion area getter the fast diffusing impurities both by means of the ion interaction and owing to the mechanical tensions near dislocations.

Another mechanism of gettering is absorption of the admixture defects by the liquid or liquidlike phase. It is known, that the balanced distribution ratio  $k_0$  in silicon for majority of impurities is less than one [66]. For instance, for copper the distribution ratio in silicon constitutes  $4 \cdot 10^{-4}$ , for gold —  $10^{-15}$ , for iron —  $10^{-15}$ . If in any part of the wafer to create a liquid phase, then its remaining part can be purified from impurities with  $k_0$ <1. Insertion into silicon of a great number of disruptions of the crystal lattice imitate the liquid-like phase [67], and during the thermal treatment this phase getter the impurities with  $k_0$  < 1 from the remaining, undisturbed part of silicon. Such upset liquid-like phase is created on the back side of the wafer during insertion into it the disruptions of the crystal lattice by the mechanical method (for instance, grinding), ion implantation of argon, high temperature phosphorus diffusion, laser irradiation, etc.

Gettering may also take place owing to extraction of the admixture defects into vacuum or gaseous phase. During the high-temperature annealing of the Si-wafers in the neutral atmosphere or in vacuum there occurs evaporation of the silicon atoms and admixture from the surface. Concentration increase of vacancies (concentration reduction of the inter-node atoms) on the surface relative to balanced in bulk results in diffusion of the inter-node atoms to the surface, reduction of the packing defects and formation in the surface layer of the defectless area. During evaporation the system «silicon—impurity» loses the volatile component, releasing silicon from the easily evaporated admixture. Addition of HCl and trichloroethylene into vapor gaseous mixture during oxidation results in the similar effect. At the high temperature the silicon atoms are pulled by the molecules of HCl, reaching the surface of partition «Si—SiO<sub>2</sub>», into the oxide layer and get oxidized there [68]. Meanwhile, concentration of vacancies on the surface increase as compared with the balanced one. Number of the extracted silicon atoms from the silicon surface into oxide and, appropriately, the surface concentration of vacancies increase with the concentration increase of HCl and the oxidation temperature [69].

The gettering mechanism may be also adsorption of the impurity defects on the developed surface. In this case the solid body surface adsorbs them, reducing its free energy. By increasing the surface area in the non-active areas of the wafer it is possible to extract the admixture defects there. By this mechanism occurs gettering of impurities by means of the porous silicon, formed on the back side of the wafer [24].

An important mechanism of gettering, that is always present during the laser or fast thermal treatment, is extraction of the impurity, distributed in the near surface area of the semiconductor wafer, on its surface with a great temperature gradient, perpendicular to the wafer. On the basis of consideration of the 1D flow of the impurity atoms, related to the temperature gradient, in [41] it is indicated, that with the preset  $\operatorname{grad} T$  the heat transfer value determines the value and direction of the impurity flow in the non-uniform temperature field. This signifies, that on all impurity atoms the force is applied, determined by the temperature gradient and directed to the wafer surface. As the surface is reflective, nearby it occurs accumulation of the impurity, which under the definite conditions may evaporate from the surface, thus purifying the surface from the admixture defects.

The mechanism, promoting transfer of the admixture defects to the surface and its subsequent evaporation, is the liquid phase re-crystallization of the silicon working surface under influence of the

laser irradiation of the nanosecond duration. During such treatment within the first 10-20 ns of the laser pulse there occurs the silicon melting, and the temperature in the flux reaches the values, far exceeding the melting temperature of the irradiated material. In such state the surface layer keeps on remaining during approximately 250 ns, which initially exceeds duration of the laser pulse. The melting edge quickly spreads into the crystal to the depth of the order of 1  $\mu$ m during the time stretch, just a little exceeding the pulse duration. Then the flux edge moves in the reverse direction to the surface, recrystallizing as it progresses in motion. Meanwhile the molten layer grasps the admixture defects, determined by such admixtures as, for instance, Fe, Ni, Cr, Cu, Na, K, C, as well as the point defects. As a result of their diffusion via the liquid flux and the re-crystallization edge force-out they emerge on the wafer surface and evaporate, thus forming the thin (about 1  $\mu$ m) surface layer, free from the admixture defects.

An important role during gettering is played by such mechanism, as a grasp of the admixture defects by the oxygen precipitates, which may be formed both with application of the special thermal treatments [39, 40] and with application of the laser irradiation [70].

The formation mechanism of the oxygen precipitates requires for its realization availability in the silicon wafers of the oxygen concentration above the critical one and performance of their thermal treatment in three stages. At the time of the first stage at the high temperaturee ( $T_1$ =1100—1200°C) depletion dominates the near surface zone with oxygen, whose process is described by the equation of the impurity diffusion from the limited source with the binding boundaries. As a result, at the expense of the oxygen evaporation, the oxygen depleted near surface area is formed. At the time of the second annealing at the low temperature ( $T_2$ =600—800°C) there occurs the homogeneous nucleation (emergence of the precipitation centers) of oxygen. At the time of the third stage at the temperature of  $T_3>900$  °C there simultaneously occurs evaporation of oxygen from the wafer surface and growth of the oxide precipitates. The clean zone is formed because of the fact, that those nuclei, which have grown at the temperature  $T_2$  and had the radius less than critical at the temperature  $T_3$ , get diluted at the time of the third annealing, and the nuclei with the radius over critical, vice versa, grow in the oxygen precipitates, which perform the role of gettering centers. Meanwhile, the distribution profile of the oxygen precipitates by thickness of the silicon wafer has such a nature, that the near surface zone of the silicon wafer becomes clean from them, and, consequently, pure from the admixture defects, which get grasped by the oxygen precipitates, lying below the clean zone [71, 72]. In the described formation model of the internal getter, the nature of oxygen precipitation almost completely is determined by the initial concentration of oxygen, incubation time of the precipitation centers origination, by sequence and modes of the thermal treatments.

In application of the continuous laser irradiation the process of gettering passes at the expense of action of two factors — curve of the silicon wafers and occurring meanwhile stretching tensions, which promote formation of precipitates in the gettering layer, ensuring the high efficiency of the puri-

fication process of the working side of the wafer from the impurity pollutions and point defects. The main cause of unavailability of the diffusion flow of admixtures from the gettering layer into the bulk of the wafer with the subsequent high temperature treatments is their capture by the oxygen precipitates, whose emergence promotes formation of the liquid phase of silicon during the laser treatment and the subsequent continuous high temperature treatment in the oxygen medium [70].

On the basis of the considered processes, passing in the silicon wafers during their purification from the admixture defects by the various methods, it is possible to highlight the following mechanisms of interaction of the point defects and polluting admixtures, owing to which gettering occurs:

- interaction of the admixture defects with the field of elastic tensions;

- electric interaction of the admixture defects amongst themselves;

- absorption of the admixture defects by the liquid or liquid-like phase;

- extrusion of the admixture defects into vacuum or gaseous phase;

- adsorption of the admixture defects on the developed surface of the solid body;

- diffusion of the admixture defects to the surface under influence of the temperature gradient through the wafer thickness;

- transfer of the admixture defects by the edge of the liquid phase re-crystallization to the irradiated surface;

- absorption of the admixture defects by the oxygen precipitates.

To the individual methods of gettering there may correspond both a single or several methods, meanwhile, the greater their number for the given method, the more efficient the process will pass of the silicon purification from the point defects and polluting admixtures.

Thus, one may conclude, that during selection of the gettering method of the silicon wafers it is necessary to consider the following:

- availability of the maximum possible number of the interaction mechanisms of the point defects and polluting admixtures, owing to which the gettering process goes on;

- possibility of the method application both at the various creation stages and during duration of the entire process cycle of ICs fabrication;

- flexibility and simplicity of the gettering centers formation in silicon;

- compatibility of the gettering process with the technological process of ICs creation.

## References

- 1. Gettering Processes in the Fabrication Technology of the Silicon Wafers / A. M. Dyachkov [and others] // Electronic Industry 2003.— Issues 3. Pages 33-40.

- 2. Pearce, C.H. Defect and contamination control in VLSI fabrication process / C.H. Pearce // Microelectronic Materials and Processes, Cactelvechio Pascoli, June 30 July 11, 1986. Kluwer Academic Publisher, 1989. P. 293-303.

- 3. Meda L., Cerofolini G.F., Queirolo G. Impurities and defects in silicon single crystal // Progress Crystal Growth and Characterization. 1987 V.15, №2. P. 97-134.

- 4. V. A. Skidanov Iron Concentration Evaluation in the P-Type Monocrystal Silicon Wafers / V. A. Skidanov // Electronic Industry 2003 Issue 3. Pages 135-138.

- 5. Mouche, L. Mechanism of metallic impurity deposition on silicon substrates dipped in cleaning solution / L. Mouche, F. Tardif, J. Derrien // Journal of the Electrochemical Society. 1995. V. 142, № 7. P. 2395-2401.

- 6. Lowell, J. Surface generation lifetime of MeV implanted Si / J. Lowell // Journal of the Vacuum Science and Technology. B. 1996. V. 14, № 1. P. 248 254.

- 7. Hasenack, C.M. Metal contamination of silicon wafers indu-ced by reactive ion etching plasmas and its behavior upon subsequent cleaning procedures / C.M. Hasenack, R.D. Mansano // Journal of the Vacuum Science and Technology. B. 1996. V. 14, № 1. P. 538-542.

- 8. Aragwal, A.M. Consistent quantitative model for the spatial extent of point defect interactions in silicon / A.M. Aragwal, S.T. Dunham // Journal of Applied Physics. 1995. V. 78, № 9. P. 5313-5319.

- 9. Lunnon, M.E. Some sources of emitter-collector shorts in bipolar transistor / M.E. Lunnon,

D.F. Allison, W.T. Stacy // Defects Silicon Proceedings Symposium, San Francisco, May 8-13, 1983.

New Jersy: Pennington, 1983 P. 463-471.

- 10. Declerck, G.J. Silicon Oxidation / G.J. Declerck // Microelectronic Materials and Process Proceedings, Castelvecchio Pascoli, June 30 Jule 11. 1989. NATO Advantage Study Institute. Dodrecht, 1989. P. 79-132.

- 11. Schmidt, P.F. Contamination Free High Temperature Treatment of Silicon and Other Materials / P.F. Schmidt // Journal of the Electrochemical Society. 1983. V. 130, № 1. P. 196-199.

- 12. Influence of the preoxidation cleaning on the electrical properties of the  $SiO_2$  layers / J.L.Prom [et al.] // IEEE Proceedings. 1988.  $N_2$  1. P. 20-22.

- 13. Domenici, K. New Aspects on Silicon Material for VLSI / K. Domenici, D.C. Ferrero, K. Pedrotti // Semiconductor Europe. 1984. № 1. P. 49-85.

- 14. Modern Methods of Gettering in Technology of Semiconductor Electronics / V. A. Labunov [and others] // Foreign Electronic Equipment 1983. № 11. Pages 3-66.

- 15. Gettering of Point Defects in Fabrication of Semiconductor Devices / G. Z. Nemtsev, A. I.

Pekarev, Yu. D. Chistyakov, A. N. Burmistrov // Reviews of Foreign Electronic Equipment. 1981.

№ 11. Pages 3-63.

- 16. Rorgonyi, G.A. Elimination of oxidation induced stacking faults by preoxidation gettering of silicon wafers / G.A. Rorgonyi, P.M. Petroff, M.H. Read // Electroch. Soc. 1975. V. 122, № 12. P. 1725-1732.

- 17. Florecasting the Depth of the Near Surface Damages in Materials of the Electronic Equipment During Their Treatment with Free Abradant / A. A. Britvin [and others] // Electronic Industry 2003 Issue 3. Pages 97-101.

- 18. Medernach, J.W. An evalution of extrinsic gettering techniques / J.W. Medernach, W.A. Wells, L. Witherspoon // Semiconductor Silicon 1986.: Proc. of the V Intern. Symp. On Silicon Mater. Sci. and Tech. / Ed.: H.R.Huff, T.Abe, B.Kolbesen. Pennington: The Electrochemical Society, 1986. V. 86, №4. P. 915-926.

- 19. Method for inducing damadge for gettering to single crystal silicon wafer: Пат. 5759087 США, МКИ Н 01 L 21/304 / Н. Masumura, М. Nakano, Н. Kudo (Япония); Shin-Etsu Handotai Co., Ltd.—US1995000435656; Заявл. 05.05.1995; Опубл. 02.06.1998; НКИ 451/041. 11с.- <a href="http://www.patents.ibm.com">http://www.patents.ibm.com</a>.

- 20. Renshi, S. Durability of mechanical damage gettering effect in Si wafers / S. Renshi // Japanese Journal of Applied Physics. 1984. V. 23, № 8, Pt.1. P. 959-964.

- 21. Physical Fundamentals of the Rapid Thermal Treatment. Gettering, Annealing of the Ion Doped Layers, RTT in the VLSI Technology / V. M. Anishchik [and others]; under general edition of V. A. Pilipenko Minsk: BSU, 2001. p. 149.

- 22. Rorgonyi, G.A. Elimination of process-induced stacking faults by preoxidation gettering of silicon wafers / G.A. Rorgonyi, P.M. Petroff, T.T. Shing // J. Electroch. Soc. 1976. Vol. 123, № 4. P. 565-571.

- 23. Influence of phosphorus induced point defects on a gold-gettering mechanism in silicon / D. Lecrosnier [et al.] // J. Appl. Phys. 1980. V. 51, № 2. P. 1036-1040.

- 24. Jozeph. Neutron activation analyses of epitaxial silicon / B. Graydon [et al.] // J. Electroch. Soc. 1971. V. 118, № 8. P. 1353-1358.

- 25. Gettering of metallic impurities by back side porous silicon / S.Roorda [et al.] // Canadian Journal of Physics. 1995. V. 73, № 1-2. P. 45-47.

- 26. Jaworska, D. The efficiency of gettering Au in n-type and p-type silicon / D. Jaworska, W. Shyszko, E. Tarnowska // Semiconductor Science and Technology. 1988. №3. P. 813-815.

- 27. Baginski, T.A. Germanium BackSide Gettering of Gold in Silicon / T.A. Baginski, J.R. Honkowski // Jornal of the Electrochemical Society. 1986 V. 133, № 1. P. 142-147.

- 28. Geipel, H.J. Critical microstructure for ion implantation gettering effects in silicon / H.J. Geipel, W.K. Tice // Applied Physics Letters. 1977. V. 30, №7. P. 325-327.

- 29. Meek, R.L. BPSG gettering effects in silicon wafers / R.L. Meek, T.E. Seidel, J. Cullis //

Jornal of the Electrochemical Society. 1975. V. 122 P.786-788.

- 30. Influence of phosphorus-induced point defects on gold gettering mechanism in silicon / D. Lecrosnier [et al.] // Journal of Applied Physics. 1980. V. 51, № 2. P. 1036-1038.

- 31. Ion-implantation gettering effect in silicon photodiode array camera target / C.M. Hsieh [et al.] // Appl. Phys. Let. 1973. V. 22, № 5. P. 238-244.

- 32. Gettering rates of various fast-diffusing metal impurities at ion-damaged layers on silicon / T.M.Buck [et al.] // Appl. Phys. Let. 1972. V. 21, № 8. P. 485-491.

- 33. Prussin, S. Ion Implantation Gettering; A Fundamental Approach. / S. Prussin // Solid State Technology. 1981. №7 P.52-54.

- 34. Ueda, 0. On the mechanism of intrinsic gettering by batterflytype defects in silicon / 0. Ueda, K. Nauka, J. Lagowski // Hat. Issues Silicon Integr. Circ. Pross. Symp. 1986. V. 71 P. 21-26.

- 35. Peibst, H. Nucleation of Oxygen Precipitations and Efficiency of Internal Gettering Centres in Czochralski Silicon / H. Peibst, H. Raidt // Physica Status Solidi (a). —1981. V. 68 P. 253—257.

- 36. Kamarou, A.A. Gettering of metal impurities to cavities formed by hydrogen and helium implantation in silicon / A.A. Kamarou, A.F. Kamarou, P. Zukowski // Ion implantation and other application of ions and electrons: III Internat. Symp. Kazimierz Dolny. Poland, 2000. P. 42.

- 37. Copper gettering at half the projected ion range induced by low-energy channeling He implantation into silicon / P.F.P.Fichtner [et al.] // Appl. Phys. Lett. 1997. V. 70 P. 732-737.

- 38. Tan, T.Y., Gardner E.E., Tice H.K. Intrinsic gettering by oxide precipitate induced dislocations in Czohralski Si / T.Y. Tan, E.E. Gardner, H.K. Tice // Applied Physics Letters. 1977. V. 30, № 4 P. 175—176.

- 39. Examination of the Formation Process of the Oxygen Precipitates in Silicon / I. V. Antonova [and others] // Physics and Semiconductor Engineering 1997. V. 31, №. 8. Pages 998-1002.

- 40. Takeno, H. Practical computer simulation techni-que to predict oxygen precipitation behavior in Czochralski silicon wafers for various thermal processes / H. Takeno, T. Otogawa, Y. Kitagawara // Journal of the Electrochemical Society. 1997 V. 144, № 12. P. 4340-4245.

- 41. V. I. Rudakov. Simulation of the Impurities Removal Process from the Semiconductor Wafers in the Uniform Temperature Field / V. I. Rudakov, A. V. Bashmakov, V. V. Ovcharov // Letters to the journal of the technical physics. 2004. V. 30, Issue 5. Pages 54-59.

- 42. I. V. Ostrovsky. Ultrasound Stimulated Low Temperature Redistribution of Admixtures in Silicon / I. V. Ostrovsky, A. B. Nadtochiy, A. A. Podolyan // Physics and Semiconductor Engineering —2002. V. 36, Issue 4. Pages 389-391.

- 43. S. V. Plytsko. Generation of the Bulk Defects in Some Semiconductors by the Laser Irradiation in the Sphere of Transparency of Crystal / S. V. Plyatsko // Physics and Semiconductor Engineering. 2000. V. 34, Issue 9. Pages 1046-1052.

- 44. S. V. Vintsents. On the Emergence Threshold of the Non-Elastic Deformations in the Near Surface Layers of Si and GaAs during the Multiple Pulse Laser Irradiation / S. V. Vintsents, A. V. Zoteev, G. S. Plotnikov // Physics and Semiconductor Engineering. 2002. V. 36, Issue 8. Pages 902-906.

- 45. M. G. Koen. Microtreatment of Materials / M. G. Koen, R. A. Kaplan, Yu. G. Arturs // TIIER. 1982. V. 70, № 6. Pages 27-35.

- 46. Hayafuji, Y. Laser damage gettering and its application to life time improvement in silicon / Y. Hayafuji, T. Yanada, Y. Aoki // J. Electroch. Soc. 1981. V. 128, № 9. P. 1975-1982.

- 47. Laser Gettering of Defects in Fabrication of the Semiconductor Devices and ICs / V. A. Gorushko [and others] // Electronic Equipment. Series 3. 1984 Issue 1. Pages 107-108.

- 48. Structural Improvement of the Semiconductor Layers by Gettering with Application of the Laser Irradiation / V. A. Plipenko [and others] // Electronic Equipment. Series 8. 1983 Issue 5. Pages 7-11.

- 49. V. A. Pilipenko. Application of the Photon Technological Processes during Fabrication of the Integrated Microcircuits / V. A. Pilipenko, Yu. P. Popov // Electronic Industry. 1988. Issue 5. Pages 3-11.

- 50. V. A. Pilipenko. Properties Control of the Thin Film Systems with Application of the Pulse Photon Treatment / V. A. Pilipenko, V. N. Ponomar, V. A. Gorushko // Engineering Physical Journal. 2003. —V. 76, № 4. Pages 95-98.

- 51. Formation of the Gettering Layers in Silicon with Application of the Continuous Laser Irradiation / D. V. Vecher, V. A. Gorushko, V. A. Emelyanov, T. V. Petlitskaya, V. A. Pilipenko, D. A. Rusakevich, V. S. Syakersky // Reports of BSUIR. 2006. № 5. Pages 5-12

- 52. Influence of Laser Gettering on the Structural and Electric Parameters of the Epitaxial Silicon Films / V. A. Pilipenko, D. V. Vecher, V. V. Ponaryadov, V. A. Gorushko, V. S. Syakersky, T. V. Petlitskaya // Bulletin of BSU. Series 1. 2007. № 2. Pages 39-42

- 53. Influence of Laser Gettering of Silicon Wafers on the Properties of the Separation Boundaries of Si-SiO<sub>2</sub> / V. A. Plipenko, D. V. Vecher, V. V. Ponarydov, V. A. Gorushko, V. S. Syakersky, T. V. Petlitskaya // Bulletin of BSU. Series 1. 2008. № 1. Pages 23-25

- 54. V. A. Pilipenko. Influence of the Laser Gettering on the Electric Parameters of the Bipolar ICs. / V. A. Pilipenko, D. V. Vecher, V. A. Gorushko, V. V. Ponaryadov, V. S. Syakersky // Reports of BSUIR. 2009. №8. Pages 63-66

- 55. N. V. Cherepnin. Physical Concepts of the Laser Annealing Mechanism of the Implanted Semiconductor Structures / N. V. Cherepnin // Review on Electronic Equipment. Series 7. 1981. Issue 8. Pages 3-25.

- 56. Surface Laser Treatment of the Silicon Wafers / V. A. Gorushko [and others] // Surface. Physics, Chemistry, Mechnics. 1984. V. 7. Pages 113-118.

- 57. Silicon Surface Properties after the Laser Treatment by Pulses of Nanosecond Duration / V. A. Pilipenko, D. V. Vecher, V. A. Gorushko, V. S. Syakersky, T. V. Petlitskaya // IPhJ. 2008 V. 81, № 3. Pages 592-595.

- 58. Lambert, I.L. The gettering of gold and coper from silicon / I.L. Lambert, M. Reese // Solid State Electron. 1968. V. 11, № 11. P. 1055-1060.

- 59. Shrinkage effect of stacking-faults during HCl oxidation in steam / H. Shibayama [et al.] // Appl. Phys. Let. 1976. V. 29, № 3. P. 136-141.

- 60. Hattori, J. HCl oxidation conditions for stacking-fault nuclei gettering and for silicon etching / J. Hattori // J. Appl. Phys. 1977. V. 49, № 5. P. 2994-2999.

- 61. Seidel, T.E. Eiectron-bean-induced current and TEM studies of stacking faults farmed by the oxidation of boron-implanted silicon / T.E. Seidel, S.E. Haszko, D.M. Maker // J. Appl. Phys. 1977. V. 48, № 12. P. 5038-5043.

- 62. Pickar, K.A. Gettering rates of various fast-diffusing metal impurities at ion-damaged layers on silicon / K.A. Pickar, J.M. Poate, T.M. Buck // J. Appl. Phys. 1975. V. 46, № 2. P. 600-604.

- 63. Yang, K.H. Minority carrier lifetime improvement in silicon through laser damage gettering / K.H. Yang, G.H. Schwittke // Phys. Stat. Sol. (a). 1980. V. 58, № 1. P. 127-132.

- 64. Sigmon, T.W. Ion-implantation gettering of gold in silicon / T.W. Sigmon, L. Cbepregi, L.M. Mayer // J. Electroch. Soc. 1976. V. 123, № 7. P. 1116-1121.

- 65. Meek, R.L. Diffusion gettering of Au and Cu in silicon / R.L. Meek, T.E. Seidel, A.G. Cullis // J. Electroch. Soc. 1975. V. 122, № 6. P. 786-792.

- 66. Shinura, F. Thermally induced defect behavior and effective intrinsic gettering sink in silicon wafers / F. Shinura, H. Tsuya, T. Kawanura // J. Electroch. Soc. 1981. V. 128, № 7. P. 1579-1586.

- 67. Ing, S.W. Gettering of metallic impurities from planar silicon diodes / S.W. Ing, R.E. Morris, L.L. Alt // J. Electroch. Soc. 1963. V. 110, № 6. P. 533-538.

- 68. Antonella, P. Denuded sone stability in a SPAD diode as a function of outdiffusion parameters / P. Antonella, R. Maufred, S. Eurichetta // IEEE Transaction Electron Devices. 1987. V. 34, N 7. P. 1486—1500.

- 69. Purification Method of the Silicon Wafers and Ingots: a. c. 1753894 USSR, MKI H 01 L 21/322. / V. A. Kharchenko, A. A. Stuk, B. V. Smirnov, E. S. Levshin, E. F. Lobanovich, A. N.

- Petlitsky (USSR).  $\mathbb{N}_2$  4797655; Declared on 28.02.90; Published on 30.06.92, Bulletin  $\mathbb{N}_2$  46 // Inventions. 1992.  $\mathbb{N}_2$  46. Page 84.

- 70. V. A. Pilipenko. Model of the Laser Gettering of the Rapid Diffusion Admixtures / V. A. Pilipenko, V. N. Ponomar, V. A. Gorushko // Engineering Physical Journal. 2005. —V. 78, № 3. Pages 107-109.

- 71. Timelag in nucleation of oxygen precipitates in silicon due to high temperature preannealing / N.Inoe [et al.] // Journal of Crystal Growth. 1987. V. 84. P. 21-35.

- 72. Homogeneous Emergence of Precipitates in Silicon / V. V. Voronkov [and others] // Crystallography. 1989. V. 34, Issue 1. Pages 199-207.